Instruction Format and Assembly Language

Machine Language Instructions. The instructions that can be decoded and executed by the control unit of a computer are represented in machine language. Instructions in this language are expressed in binary, and a typical format is shown in Figure 5.14.

The operation code field (referred to by the shorthand phrase op code) is a unique unsigned integer code assigned to each machine language operation recognized by the hardware. For example, 0 could be an ADD, 1 could be a COMPARE, and so on. If the operation code field contains k bits, then the maximum number of unique machine language operation codes is 2^k.

The address field(s) are the memory addresses of the values on which this operation will work. If our computer has a maximum of 2^N memory cells, then each address field must be N bits wide to enable us to address every cell because it takes N binary digits to represent al addresses in the range 0 to 2^N— 1. The number of address fields in an instruction is typically ranges from 0 to about 3, depending on what the operation is and how many operands it needs to do its work. For example, an instruction to add the contents of memory cell X to memory cell Y requires at least two addresses, X and Y. It could require three if the result were stored in a location different from either operand. In contrast, an instruction that tests the contents of memory cell X to see whether it is negative needs only a single address field, the location of cell X.

To see what this might produce in terms of machine language instructions, let's see what the following hypothetical instruction would actually look like when stored in memory:

ADD X, Y Add contents of memory addresses X and Y and put the sum back into memory address Y.

Let's assume that the op code for ADD is a decimal 9, X and Y correspond to memory addresses 99 and 100 (decimal), and the format of instructions is

A decimal 9, in 8-bit binary, is 00001001. Address 99, when converted to an unsigned 16-bit binary value, is 0000000001100011. Address 100 is : 0000000001100100. Putting these values together produces the instruction ADD X, Y as it would appear in memory:

00001001 0000000001100011 0000000001100100

This is somewhat cryptic to a person, but is easily understood by a control unit.

For clarity, we will not show these instructions in binary, as we did earlier. Instead, we will write out the operation code in English (for example, ADD, COMPARE, MOVE); use the capital letters X, Y, and Z to symbolically represent binary memory addresses; and use the letter R to represent an ALU register. Remember, however, that this notation is just for convenience. All machine language instructions are stored internally using binary representation.

The set of al operations that can be executed by a processor is called its instruction set, and the choice of exactly what operations to include or exclude from the instruction set is one of the most important and difficult decisions in the design of a new computer.

he machine language operations on most machines are quite elementary, and each operation typically performs a very simple task. The power of a processor comes not from the sophistication of the operations in its instruction set, but from the fact that it can execute each instruction very quickly, typically in a few billionths of a second.

One approach to designing instruction sets is to make them as small and as simple as possible, with perhaps as few as 30-50 instructions. Machines with this sort of instruction set are called reduced instruction set computers or RISC machines. This approach minimizes the amount of hardware circuitry (gates and transistors) needed to build a processor. The extra space on the chip can be used to optimize the speed of the instructions and allow them to execute very quickly. A RISC processor may require more instructions to solve a problem (because the instructions are so simple), but this is compensated for by the fact that each instruction runs much faster so the overall running time is less. The opposite philosophy is to include a much larger number, say 300-500, of very powerful instructions in the instruction set. These types of processors are called complex instruction set computers, or CISC machines, and they are designed to directly provide a wide range of powerful features so that finished programs for these proces- sors are shorter. Of course, CISC machines are more complex, more expensive, and more difficult to build. As is often the case in life, it turns out that compromise is the best path—most modern processors use a mix of the two design philosophies.

Machine language instructions can be grouped mainly into four basic classes called data transfer, arithmetic, compare, and branch.

1. Data Transfer

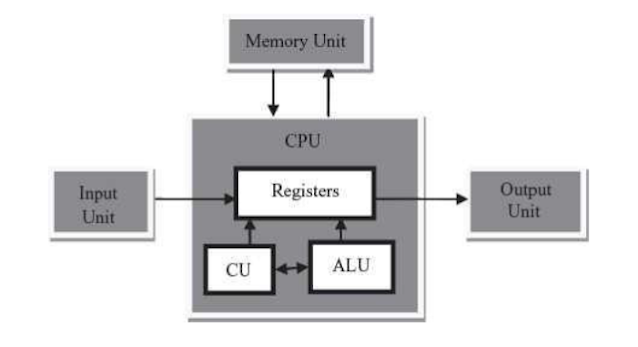

These operations move information between or within the different components of the computer—for example:

Memory cell - ALU register

ALU register — memory cell

One memory cell — another memory cell

One ALU register — another ALU register

All data transfer instructions follow the nondestructive fetch/destructive store principle described earlier. That is, the contents of the source cell (where it is now) are never destroyed, only copied. The contents of the destination cell (where it is going) are overwritten, and its previous contents are lost.

Examples of data transfer operations include

Operation Meaning

LOAD X Load register R with the contents of memory cell X.

STORE X Store the contents of register R into memory cell X.

MOVE X Y Copy the contents of memory cell X into memory cell Y.

2. Arithmetic

These operations cause the arithmetic/logic unit to perform a computation. Typically, they include arithmetic operations like +, —, X, and /, as well as logical operations such as AND, OR, and NOT. Depending on the instruction set, the operands may reside in memory or they may be in an ALU register.

Possible formats for arithmetic operations include the following examples. (Note: The notation CON(X) means the contents of memory address X.

Operation Meaning

ADD X ,Y, Z Add the contents of memory cell X to the contentsof memory cell Y and put the result into

ADD X,Y Add the contents of memory cell X to the contents of memory cell . Put the result back into

Other arithmetic operations such as SUBTRACT, MULTIPLY, DIVIDE, AND, and OR would be structured in a similar fashion.

3. Compare

These operations compare two values and set an indicator on the basis of the results of the compare. Most Von Neumann machines have a special set of bits inside the processor called condition codes (or a special register called a status register or condition register); these bits are set by the compare operations. For example, assume there are three 1-bit condition codes called GT, EQ, and LT that stand for greater than, equal to, and less than, respectively. The

Operation Meaning

COMPARE X Y Compare the contents of memory cell X to the contents of memory cell Y and set theCondition. How the Condition Codes Are Set

CON(X)>CONY) GT=1 EQ=0 LT=0

4. Branch

1, then after finishing the instruction starting in address i, the control unit executes the instruction starting in address i + k. In the following discus- sions, we assume for simplicity that each instruction occupies one memory cell.) The branch instructions disrupt this sequential mode.

Typically, determining whether to branch is based on the current set- tings of the condition codes. Thus, a branch instruction is almost always preceded by either a compare instruction or some other instruction that sets the condition codes. Typical branch instructions include

Operation Meaning

(JUMPEQ and JUMPLT would work similarly on the other two condition codes.)

HALT Stop program execution. Don’t go on to the next instruction.

The instructions presented here are quite simple and easy to understand. The power of a Von Neumann computer comes not from having thousands of built-in, high-level instructions but from the ability to combine a great number of simple instructions into large, complex programs that can be executed extremely quickly. Figure 5.15 shows examples of how these simple machine language instructions can be combined to carry out some of the tasks.

Modern computers uses different processors and the instruction set depends on the processor used. Some additional instructions in the instruction set are

Boolean Logic Instructions

Most modern instruction sets provide instructions for performing Boolean algebra. Com- monly included are a NOT instruction, which inverts the bits on a single operand, as well as AND, (inclusive) OR, and EXCLUSIVE-OR instructions, which require two source arguments and a destination.

Single Operand Manipulation Instructions

In addition to the NOT instruction described in the previous paragraph, most computers provide other convenient single operand instructions. Most of these instructions operate on the value in a register, but some instruction sets provide similar operations on memory values as well. Most commonly, the instruction set will contain instructions for NEGATing a value, for INCREMENTing a value, for DECREMENTing a value, and for setting a register to zero. There are sometimes others. On some computers, the increment or decrement instruction causes a branch to occur automatically when zero is reached; this simplifies the design of loops by allowing the programmer to combine the test and branch into a single instruction.

Shift and Rotate Instructions

Shift and rotate operations have been mentioned previously as a means to implement multiplication and division. Shifts and rotate operations have other programming appli- cations, and CPU instruction sets commonly provide a variety of different shift and rotate instructions for the programmer to use. As shown in Figure 7.11, shift instructions move the data bits left or right one or more bits. Rotate instructions also shift the data bits left or right, but the bit that is shifted out of the end is placed into the vacated space at the other end. Depending on the design of the particular instruction set, bits shifted out the end of the word may be shifted into a different register or into the carry or overflow flag bit, or they may simply ‘‘fall off the end’’ and be lost.

Two different kinds of shifts are usually provided. The data word being shifted might be logical or it might be numeric. Logical shift instructions simply shift the data as you would expect, and zeros are shifted in to replace the bit spaces that have been vacated. Arithmetic shift instructions are commonly used to multiply or divide the original value by a power of 2. Therefore, the instruction does not shift the leftmost bit, since that bit usually represents the algebraic sign of the numeric value—obviously the sign of a number must be maintained. Left arithmetic shifts do not shift the left bit, but zeros replace the bits from the right as bits are moved to the left. This will effectively double the numeric value for each shift of one bit. On the other hand, right arithmetic shifts fill the space of moved bits with the sign bit rather than with zero. This has the effect of halving the value for each bit shifted, while maintaining the sign of the value. It may not seem obvious to you that this works correctly, but it becomes more apparent if you recall that negative numbers in complementary arithmetic count backward starting from the value −1, which is represented in 2’s complement by all ones.

Rotate instructions take the bits as they exit and rotate them back into the other end of the register. Some instructions sets include the carry or overflow bit as part of the rotation. Some CPUs also allow the rotation to take place between two registers. Rotate instructions can be used to exchange the 2 bytes of data in a 16-bit word, for example, by rotating the word by 8 bits.

Comments

Post a Comment